昨夜作りかけたディスプレイコントローラだが、ちょこちょこっとデバッグして、画面が映るようになった。しかし、VGA の解像度に充分な容量のメモリは (DRAM が動かない限り) ないので、いまのところ適当なパターンを作る回路が仕込んであり、スイッチでそれを切り替えて遊べる、みたいな感じ。

で、テキスト VRAM みたいなのがあって、文字を表示できたらいいかなー、と思ったので、現状のパターン発生回路の出力にテキストをスーパーインポーズできるような仕掛けを作ることにした。フォントを作っちゃえばあとはなんとかなるだろ、と思うのだが、甘いかな。とりあえず、テキストに簡単な属性がつけられるといいなー、と思って、本棚から何年ぶりかで「PC-9800シリーズ テクニカルデータブック」を引っ張り出してみた。テキストVRAMの属性ビットのところをみると、

– R

– G

– B

– VL (Vertical Line)

– UL (Under Line)

– RV (Reverse)

– BL (Blink)

– ST_ (Secret)

だそうだ。Secret は実装しなくてもいいか。UL は 4 pixel 右にずれる仕様で、つまり、VL と合わせると罫線としても使えるようになっている。いまさらだけど、98 かっこいいな!

で、XC3S700AN の Block RAM は 20 個ある、というのを前提に仕様を整理してみることにする。

CG (Character Generator) に必要なメモリは、1文字 8×16 で 16bytes. カタカナだけの 8bit コードを全部サポートすると、4kB 必要になるが、ASCII だけの 7bit コードなら、2kB だから、BlockRAM ひとつにちょうど収まる (こう考えてみると、CG というのはけっこう大きな ROM が必要で、ましてや漢字をサポートするというのは、16×16 だとしても 32bytes/character なわけで、ひと昔前ならば一大事業だと思う)。

VRAM のほうは、1文字 8bit で、80×25 でちょうど 2kB. これだと 640×400 しか使い切れない (NEC の気持ちがわかった気がするぞ!)。キャラクタの高さを 16 ドットにすると、80×30 まで入るわけで、これだと 2400bytes 必要であり、352バイトはみ出してしまうが、さすがにこれだけのために BlockRAM をもうひとつ使うのはなんかもったいないので、attribute を 4bit に圧縮して、BlockRAM の後半をこれに使うことにした。RGB + UL でいいかな。

VRAM のアドレッシングは、VGA コントローラから現在の X 座標と Y 座標の値が出てくるので、X (8 pixels/character) は下の 3 bit を切り捨てて、Y (16 pixels / character) は下の 4bit を切り捨ててやれば、キャラクタ座標になるわけだ。しかし、ここからアドレスに変換するところが実に問題で、80 を掛ける、というのはけっこうしんどい。そこで、text + attribute で、一行あたり 120 bytes だから、128bytes / line を割り当てることにした。こうすると、4kB のメモリには 32 行分乗ることになり、30行の画面には充分である。結局のところ、アドレス計算は、

assign TEXT_A[11:0] = {VGA_Y[9:4], VGA_X[9:3]};

みたいな感じでできる。Attribute のほうは、2 桁分が 1 バイトで読めてくるので、そこはちょっと工夫が必要だが、たいしたことはない。

CG は、アドレスの上位 7 ビットが文字コードで、下位 4 ビットが Y 軸。

これが終わったら、とりあえず文字の表示とかが FPGA 単体でできるようになるわけなので、学生の教育用に UART と Ethernet の MAC くらいは作りたいが、Ethernet MAC は大変そうだなあ。

月: 2008年11月

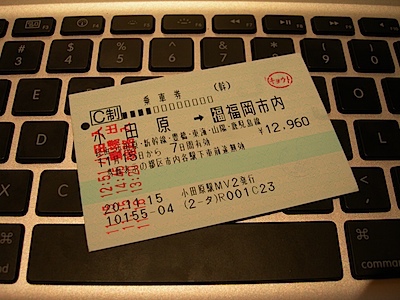

折尾駅

九州いってきた

くまー

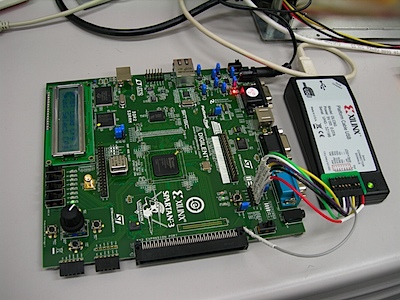

SPARTAN-3AN Startar Kit

Nokia撤退

Nokia は国内キャリア向けの端末供給を中止するそうだ。asahi.com によれば、「世界的に厳しい経済傾向の中では、日本独自の製品展開のために投資を続けることはできないと判断した」からとのこと。

iPhone に乗り換えるまで、ずっと Nokia の端末使ってたんだよ。よかったのになー。というか、日本のキャリアから供給されるほかの携帯電話は、Nokia とか Apple のそれに比べれば、所詮オモチャでしかないというか。携帯電話キャリアのメールアカウントにしかアクセスできないとか、パソコンと電話帳やスケジュールが同期できないとか、そんなのいまどき使い物にならないでしょう。ユーザがそんなので満足しちゃって、余計な機能に踊らされてるから、日本だけ変な方向に行くんだと思う。

CNET Japan か何かで、「日本の携帯電話の方向性がガラパゴスの生物みたいに独自の方向性にいったのをみんな批判するけど、その方向のまま頑張ればいい」みたいな記事を見かけたが、そりゃ、日本の電機メーカーが携帯電話でビジネスしなくていいなら、それでいいわけだけれど、実際のところ他の分野では最強の日本の電機メーカーも、携帯電話では国内キャリアの要求を呑むために必死になりすぎて、国際的なシェアでは Nokia や Motorola に遠く及ばないわけで。日本の携帯電話キャリアがこのままの姿勢を続けたら、この分野で日本の未来はない… かもしれない。

Yukiya in Bouygues Telecom!!

エキップアサダ・梅丹本舗 GDR の新城選手が、なんと Bouygues Telecom に移籍ですよ。Discovery にいた別府選手に次ぐ若手日本人選手の登場だ。すげーな!

欧州チームでの活躍に期待しております。

リコンフィギャラブルシステム研究会: Nov.18, 2008

[ The End of Moore’s Law and the Future of Computing Systems, Probably ]

Value of Information and Probabilistic System Design

Things are going to be harder in < 22nm process…

How about relaxing the requirement for 100% correctness for devices?

Human perception is not 100% correct; invest power to important stuff, less power to others; non-uniform investment / scaling.

Current optimization vectors: speed, area, and power.

Proposed: speed, area, power, and correctness.

Probabilistic SoC: ex) deterministic host microprocessor + probabilistic application specific co-processor

[ CベースプログラマブルHWコア「STPエンジン」の現状と展望 ]

NEC 本村さん。

STP = Stream TransPose.

Programmable arithmetic array + DMA engine.

演算器アレイのところは DRP を継承、ただし動的再構成技術の位置づけを見直しし、内部アーキテクチャも変更。

画像変倍で Core2Duo に対して x15 throughput, 1/10 power.

いまは 90nm で、40nm のを開発する。

[ 書換え可能な二変数関数の数値計算回路について ]

1変数関数を組み合わせてつくるのではなく、2変数関数をダイレクトに作る手法。

区分多項式近似: 定義域を複数の区間 (領域) に分割して、それぞれを近似式で表現。定義域の効率的な分割法 (=最小区間数) が重要。

1変数では区間数最小の不等区間分割をすることは比較的容易。

2変数では… 最適な領域の形が四角いとは限らない!!

さすがに四角くないのはハードウェア的にしんどいので、再帰的に4等分しながら、許容誤差を下回るまでがんばる、という方法。

浮動小数点のニーズが多いと思うが、移行は難しいでしょうか (安永先生)

→ 演算器の遅延などが大きくなるのが問題。係数表を引くところも大変そうだ。

[ An adaptive pattern recognition hardware with on-chip dynamic and partial reconfiguration ]

DDI: Direct Data Implementation = たとえば顔画像のデータをそのまま回路に実装して認識に使う。輝度値を 3bit 表現にして、画素数を減らして… とすると、組み合わせ回路だけで回路にハードコードされた画像と入力画像のマッチングをとることができる。

そうすると、この「ひとつの画像とのマッチングをとる回路」をたくさん並べてやることで、入力がどのカテゴリに属するか、といったことを一発で調べられる。

でも、組み合わせ回路のところを毎回合成したりするのは大変だから、これをなんとかしたい。これを、ICAP とかは使わずに、動作中に動的再構成できるようにする。LUT を SR として instantiate し、PowerPC から制御することで実現。オンチップで最適な d サイズを探索し、コンフィギュレーションを行うことができる。

4bit 精度で、9×20 pixels の画像を9 枚 DDI で実装。ターゲットは XC2VP30.

ASICを使ってやる場合との違いは? (東北大 宮本先生)

→ サンプルデータに対して直接の回路化を行うことができる。

[ A Novel network optimization method using On-Chip Virtual Network on Dynamically Reconfigurable processor DAPDNA-2 ]

仮想ネットワークを DAP/DNA-2 上に構築して、トラフィック変動を求めることで、理想的な転送経路を探索する。

仮想ノードと仮想リンクをそれぞれ複数のPEを使って構築し、パケットの流れを再現する。リンクはリンクコストに相当する遅延を発生。

6ノードまで1チップに入る。それより大きいのを扱うときは、途中にメモリをはさんで切り分け。

計算をせずに経路を求められるので速い。

自動的にコンフィギュレーションを生成する方法を考えたりしている。

混雑度とかで遅延がかわると思うのだけど、そのへんは一定? (おさな)

→ そういうのはリンクコストに反映されます (あとでこれは将来の実装の話だ、といわれました。いまは固定だそうです) 。だいじょうぶ。

ものすごくノード数が大きなネットワークになっても、Dijkstra とかより有利? (堀先生)

→ 実際にパケットを流しているので、リンクコストの変更とかそういうことにも対応できる点が数学的な手法よりも有利。

複数の context にわかれたときの、reconfiguration のオーバーヘッドはどれくらい? (安永先生)

→ 数クロックかそれくらいだと思います。

全部のパケットが流れ終わってからコンテキストを切り替えるの? それを検出する仕掛けとか、メモリに全部入るまで待つとしたら、それがボトルネックにならないか? (梶原さん)

→ (1) 最短経路を求めるので、ひとつしか覚えておかなくても OK なので、それでサボれるかもしれないが、トポロジが複雑になるとちょっと難しいかも。(2) ループ検出機能をつけて、さくっとパケットが出て行くようにすれば幸せかも。といったことを考えている。

[ An improvement of Black-Diamond compiler for representing target dynamically reconfigurable architecture ]

Black Diamond は retargettable なコンパイラだが、その architecture description のファイル生成を GUI でできるようにしたぜ、という話。

最初のターゲットの場合は「たったの1万行だったから」手で書いたそうです。恐れ入りました。そのほかの2つのターゲットはこのツールで作り、5万行とかそれくらいのサイズ。

Retargettable なコンパイラを作る、その研究のゴールはどこ? という安永先生の質問が出たところで時間切れになりました。

[ DRP向け拡張C言語を使用した画像処理回路自動生成実験 ~ DAPDNA用ハードウェア自動生成言語DFC-その課題と対策 ~ ]

富士ゼロックスの人。DAP/DNA イケイケですね。

DFC というコンパイラの話。これって IPFlex が作っているのかな?

[ サイドチャネル攻撃に対する標準評価ボードSASEBOとツールの開発 ]

暗号ハードウェアに関するセキュリティ要件 (ISO/IEC 15408, FIPS140-2 = ISO/IEC 19790)。日本では JIS として承認されている。しかし、これらは再度チャネル攻撃に対応しておらず、各メーカーが独自にやっているのが現状。

で、ちゃんと規格化するには共通の評価基盤が必要。

暗号の種類とか攻撃のしかたは人間が (評価基準としてクリアしなければならないものを) きめるの? (泉先生)

→ はい。

ボードが悪い人に渡ると悪用されると思いますが、どうでしょう。(名古屋先生)

→ 評価ツールのほうが広まるといけないので、ここは厳しくしようとしているところです。

対策のしかたはたとえばどういうのがある?

→ ランダムな電力消費をする回路をつけるとか、信号線を differential にすることで消費電力プロファイルを均一化したり。

対策方法がわかると攻撃方法も進歩する?

→ それがあるので、EU は規格化に慎重。

リコンフィギャラブルシステム研究会: Nov.17, 2008

[ 反転・非反転ダイナミック転光再構成アーキテクチャのエミュレーション試験 ]

静岡大の渡邊先生の学生さん。

ダイナミック光再構成アーキテクチャ: SPD で受けた信号をメモリに蓄えるのではなく、SPD の接合容量をメモリとして用いることでメモリを省略し、面積を削減する。試作に成功している。

差分光再構成アーキテクチャ: 再構成速度を向上するにはコンテキストの輝度を上げる必要がある。これにはコンテキストの明点を削減するのが効果的で、差分再構成が効果的。

反転 SPD は、複数のビットをまとめてひっくり返すのに使い、照射ビット数の削減に役立つ。メモリがある場合には簡単だが、メモリなしのダイナミック光再構成アーキテクチャに適用。

実験で使ったチップはメモリがついているが、それを無効化して使った。0.35um プロセスのチップで、波長 850nm のレーザー。再構成時間は 1.22 倍向上。

前の発表よりも再構成時間が延びている気がしますが、方式をかえたから? (名古屋先生)

→ 使っているレーザーの出力が弱いのが原因で、前の実験と同じレーザーを使えば nsec オーダーになるはず。

プロセスが縮んだら密度があがるの? SPD の間隔が重要そうですが (大阪市立大・牧野先生)。

→ まだまだいけます。いま使っている SPD は大きいですし。

[ 光再構成型ゲートアレイのホログラム部の組み立て精度について ]

ホログラムとチップがちゃんと正しい角度で入らなかったことを想定して、ホログラム側でそれを補償できるか、という実験。

ずれがわかっていればできる、ということだと思うが、どうやってそれを検出してホログラムを選択するのか? (NEC 梶原さん etc)

→ 計測手段がなくても、いくつかホログラムを作っておいて、それを取り替えて試すことで再構成できるようになる、というのがメリット。組み立て後にホログラムを差し替えられる、という前提。

再構成エラーとか (ビットが欠けてしまうとか) は考えない?

→ それはもちろんあると思うが、そのあたりまで含めて総合的に対応のしかたを提案していきたい。

一枚目のコンテキストをいろいろやってずれを検出して、二枚目以降のコンテキストを書き込むときはそれで求めた誤差を使えばいいのか。なるほどー。

[ 低エネルギーを目的とした大規模リコンフィギャラブルプロセッサアレイSMAの予備評価 ]

Silent Mega Array.

CREST のやつ。エネルギー消費を 1/100 にしたい。

細粒度 power gating を用いた CPU (Geyser) を作った。

でも、SoC で embedded CPU の消費エネルギーはわずかなので、次は SoC 中の汎用アクセラレータがターゲット?

DR の消費電力解析:

– 効率は DSP の 1/8 – 1/10 くらい

– 動的 reconfiguration は無駄が大きい

– クロック分配も

解決策:

– とにかくアレイを大きくして詰め込んで、使わないところは power gate すれば?

– 組み合わせ回路とレジスタ部を分離して、組み合わせ回路のところだけ電圧を落とす

PE array は組み合わせ回路のみでレジスタをもたない。PE array の下にレジスタファイル。PE は粗粒度で、MuCCRA から持ってきた。

16×7 PE で、65nm の 8mm 角。

PE 1段あたり 5.8nsec 、SE 1.2nsec の遅延。

2次元 DCT が 16 clk, 10MHz くらいで動きそう。

MuCCRA-1 の 4.8 倍速い。

電圧制御可能な部分の面積は 87% 。

[ マルチコンテキスト型リコンフィギャラブルプロセッサにおけるデータ並列タスクの処理法 ]

井口先生 @ JAIST のところ。

DRP-1 だ!

DR なチップを使って処理をするには SIMD が有効だが、SIMD array に充分なデータを供給するのは入出力ポートの制約があって、ちょっと大変。ストリーミングだと、入力・処理・出力・入力… となり、入出力がしんどいが、これをパイプライン的に行うことで解決。

DRP-1 のタイルを、IT: Input Tile, PT: Processing Tile, OT: Output Tile に分ける。IT は外部からの入力、OT は外部への出力を行う。それぞれのタイルは独立して動作させ、処理と入出力を常にオーバーラップして行うことで、入出力のオーバーヘッドを隠蔽。

DRP じゃなくても使えると思うんですが (NEC 梶原さん)

→ そうです。DRP の場合は部分再構成が簡単にできることと、コンテキストスイッチができることがあるので、より有効です。

IT とか OT とか PT は、これ以上分割してパイプラインにはできない? (名古屋先生)

→ 難しそうです。

[ 粒度可変論理セル向けローカルインタコネクト構造の提案と評価 ]

VGLC は 21 本も入出力ピンがあり、接続が大変そう。

セルのアーキテクチャ自体をいじるのは大変なので、VGLC と connection block の間に LCB というのを入れて、信号数を削減することにする。

素直に作ったら、VGLC が 682Tr に対して LCB が 3484Tr と、大きくなりすぎてしまった!

削減する方法を検討して、4種類を実装。

LCB を入れることでどれくらいハッピーになれるのでしょうか (名古屋先生)

→ まだ外部配線などの評価ができていないので、どうなるかはわかりません。

入れないほうがいい、ということもありうる?

→ 条件によってはそうなります。外部配線をどれくらい入れるか、とかがまだ決まっていないので一概には言えないが、外部配線をたくさん用意した場合には LCB が必要なのではないかと思う。

[ Turnモデルに基づく二次元トーラス網の適応ルーティング ]

2D mesh 向けの、North First ルーティングを 2D torus に適用するためのNF+1 というルーティング手法の提案。

むむー、わしゃこういうのは苦手じゃけー、みんなかっこよく見える。

[ 階層型相互結合網における適応型ルーティングのハードウェア実装コストの検討 ]

オンチップマルチプロセッサ向けの階層型相互結合網 TESH に適応型ルーティングを適用する、というお話。

TESH の一番下は mesh. それをいくつか torus でつなぎあわせた形。

制御回路を VHDL で実装し、FPGA をターゲットとして評価。ルーティングアルゴリズムの実装を追加したことによる HW 量の増加は少ない。

ターゲットデバイスは何? (ふんがさん)

→ わかりません (なんだってー!!)

ISE Webpack だから SPARTAN かなぁ。でも初代かなあ。

シミュレータでの性能評価と実装での性能評価に差があったりする? (宇都宮大 森さん)

→ 今回はルータに入ってから出るまでの時間の評価なので、いままでやっていたものとは違う (という趣旨であってるかな)

[ FPGAのスイッチマトリクスを対象とするソフトエラー対策 ]

配線要素のエラーを検出する必要もあるよね。

– 3重化多数決論理パストランジスタ (MAJ: 既存手法)

– ASRAM (asymmetric SRAM) を使う (提案手法)

など。

パストランジスタを二重化したりしても、MAJ は自乗のオーダーなので非常に強くて、なかなか勝てない。しかし、メモリを二重化することで間違って on になる確率、off になる確率ともに改善。実際の configuration bit の 0/1 の偏りを考えると、ASRAM でも充分いける。2重化だと、トランジスタ数でもMAJに勝てる。3重化はさすがにダメ。

宇宙とか地上とかは想定されていますか? (尼崎先制)

マルチビットSEU を想定されている?

→ はい

FPGA では配線部がほとんどになっているわけだが、それを多重化するということは現実的なのでしょうか?

→ 難しいのではないか、と思うのでこれから評価をしていきたい。

[ 高性能差分法計算のためのFPGAアレイにおけるFPGA間通信機構の検討 ]

差分法を解くためのアレイ型計算機を FPGA で作る。

パイプラインが複数の FPGA にまたがるのと違って、PE がいくつか FPGA に入っていて、隣接 PE / FPGA 間では差分をとるための通信だけをすればいい、というのだとバンド幅が少なくてもすむのかな…

PE の中身は積和演算。

パイプラインが FPGA 間にまたがる場合と、PE がうまく FPGA に収まる場合は全然違う? (おさな)

→ そりゃそうです。PE のなかのパイプラインはぎっしり詰まってるし、制御信号もあるし… 今回の実装は、PE の中身が積和演算なので、わりとうまくいっているけれど。

あーあーあーあーあー、そうだよなー。

そううまくはいかないよなー。むー。

しかし、粗粒度デバイスみたいな感じだが、そういう単位で PE を作って何とかする、というのはヒントになったような、ならなかったような。

体温計

ずっと水銀体温計を使ってたのだが、見あたらないので買いに行った。

デジタルですよデジタル。

なんか信用ならないが、水銀のやつは時計見てないとちゃんと測れない、という問題があり、つい10分とか20分くわえたままにしてしまうので、これはお気軽でいいね。

でも、水銀体温計ってまだ売ってるのね。